Total No. of Questions—8]

[Total No. of Printed Pages—3

| Seat |  |

|------|--|

| No.  |  |

[4857]-1083

## S.E. (I.T.) (First Semester) EXAMINATION, 2015

## DIGITAL ELECTRONICS AND LOGIC DESIGN

| (2012 PATTERN)                     |                |                                                                                                                                       |                |  |  |

|------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| Time: Two Hours  Maximum Marks: 50 |                |                                                                                                                                       |                |  |  |

| N.B. :                             | - ( <i>i</i> ) | Answer Q. No. 1 or Q. No. 2, Q. No. 3 or Q. No. 4, Q or Q. No. 6, Q. No. 7 or Q. No. 8.                                               | . No. <b>5</b> |  |  |

|                                    | (iii)          | Neat diagrams must be drawn wherever necessary.  Figures to the right side indicate full marks.  Assume suitable data, if necessary.  |                |  |  |

| <b>1.</b> (a)                      | (i)<br>(ii     | onvert the following numbers, show all steps: $ (2598.675)_{10} = ( )_{16} $ $ (110101.101010)_2 = ( )_8 $ $ i) (A72E)_{16} = ( )_8 $ | [6]            |  |  |

| ( <i>b</i> )                       | ) Di           | raw and explain CMOS Non-inverting buffer. $Or$                                                                                       | [6]            |  |  |

| 9 ( )                              | , D            |                                                                                                                                       | [0]            |  |  |

**2.** (a) Design full Subtractor using Decoder IC 74138. [6]

(b) Explain the following TTL characteristics. [6]

- (i) Noise Immunity

- (ii) High level input voltage  $(V_{IH})$

- (iii) Figure of Merit

| 3.         | ( <i>a</i> ) | What is race around condition? Explain with the help of timing      |

|------------|--------------|---------------------------------------------------------------------|

|            |              | diagram. How is it removed using Flip-flop. [7]                     |

|            | ( <i>b</i> ) | Draw and explain 3-bit ring counter. [6]                            |

|            |              | Or                                                                  |

| 4.         | (a)          | Design a sequence generator to generate the sequence10110           |

|            |              | using IC 74194. [7]                                                 |

|            | ( <i>b</i> ) | Design MOD-11 Up counter using IC 74191. [6]                        |

| <b>5</b> . | (a)          | Design the following functions using PLA. [6]                       |

|            |              | $F1 = \Sigma m (1, 3, 5)$                                           |

|            |              | $F2 = \Sigma m (5, 6, 7)$                                           |

|            | ( <i>b</i> ) | Draw and explain block diagram of CPLD. [6]                         |

|            |              | Or                                                                  |

| 6.         | (a)          | Explain the difference between CPLD and FPGA. [6]                   |

|            | ( <i>b</i> ) | Design 4: 1 Multiplexer using PAL. [6]                              |

| 7.         | (a)          | Explain the difference between data flow and behavioural            |

|            |              | modeling. [7]                                                       |

|            | ( <i>b</i> ) | Write entity and architecture of D Flip-flop with clear input       |

|            |              | using behavioural modeling. [6]                                     |

|            |              | Or                                                                  |

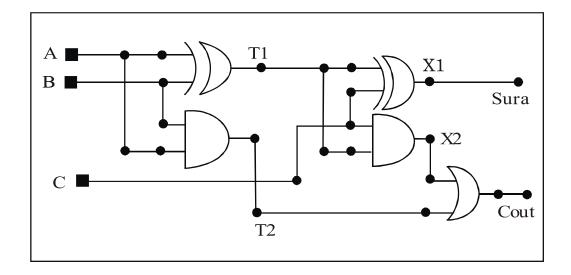

| 8.         | (a)          | Write entity and architecture of following circuit using structural |

|            |              | modeling. [7]                                                       |

(b) What is VHDL? Draw the structure of VHDL module and explain various components of it. [6]

www.sppuonline.com